Data Sheet, August 2000

C505 C505C C505A C505CA 8-bit Single-Chip Microcontroller

# Microcontrollers

Never stop thinking.

Edition 08.00

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 8/16/00. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# C505 C505C C505A C505CA 8-bit Single-Chip Microcontroller

Microcontrollers

Never stop thinking.

| C505/C5050<br>Revision Hi       |                                 | 05CA Data Sheet<br>Current Version : 08.00                                                                                                              |

|---------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Previous Re                     | leases :                        | 06.00, 07.99, 12.97                                                                                                                                     |

| Page<br>(in previous<br>version | Page<br>(in cuttent<br>version) | Subjects (major changes since last revision)                                                                                                            |

| General                         |                                 | C505CA-2R and C505A-2R included                                                                                                                         |

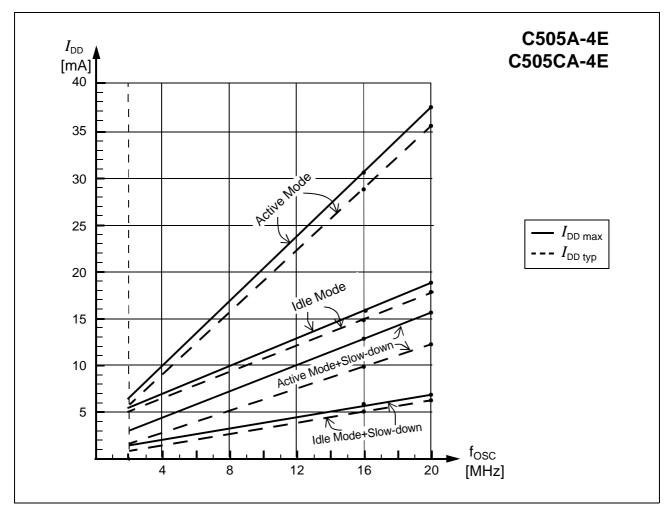

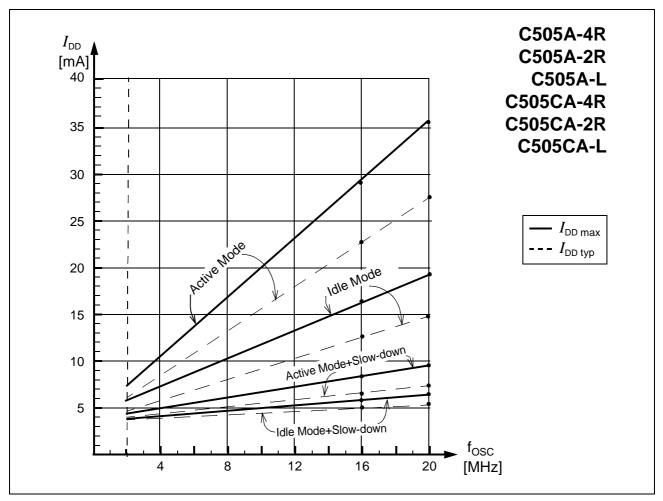

| several                         | several                         | for C505(C)A-4R/C505(C)A-2R/C505(C)A-L only: $I_{DD}$ max. values added and $I_{DD}$ typical values changed to only 1 digit after decimal point         |

| 24                              | 24                              | VR2 value for first step corrected from 31 <sub>H</sub> to 21 <sub>H</sub>                                                                              |

|                                 |                                 | Subjects (major changes from revision 07.99 to revision 06.00)                                                                                          |

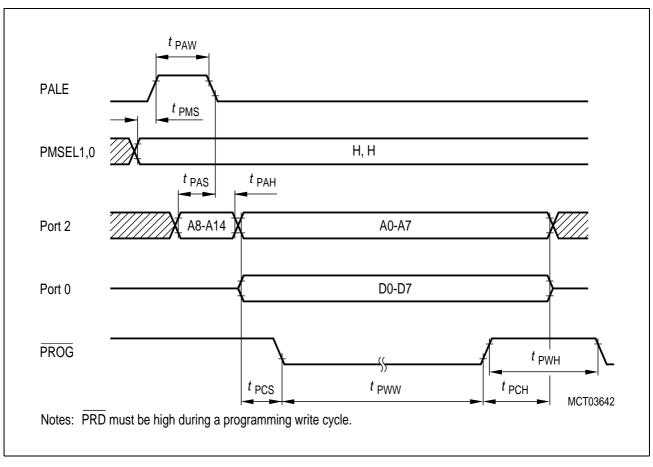

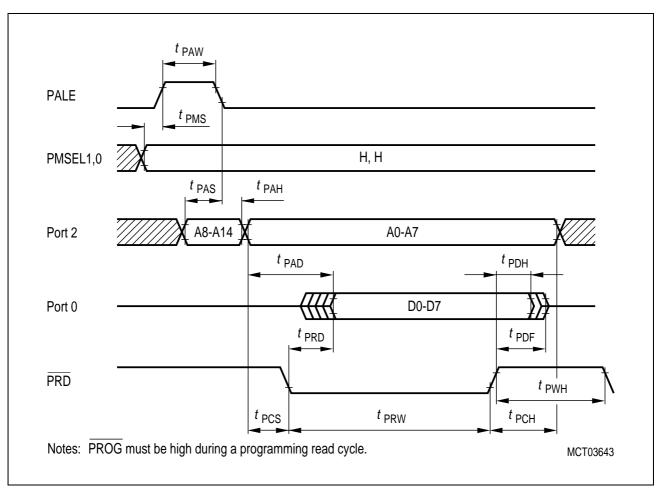

| 76                              | 76                              | Term ALE corrected by PALE in table "AC characteristics of<br>Programming Mode"                                                                         |

| 58                              | 58                              | Input high current to RESET pin added (tested for C505CA-4R, C505CA-<br>L and C505A-4R only)                                                            |

| 59,63                           | 59,63                           | I <sub>DD</sub> typical values for C505(C)A-4R/L updated                                                                                                |

| 2,57 2,57                       |                                 | Max. operating freq. of 20 MHz with 50% duty cycle for SAH, SAK temperature ranges updated for all devices except C505-L, C505-2R, C505C-L and C505C-2R |

|                                 |                                 | Subjects (major changes from revision 12.97 to revision 07.99)                                                                                          |

| general                         |                                 | Versioins C505A-4R, C505A-L, C505CA-4R and C505CA-L included. $V_{CC}$ and $I_{CC}$ replaced by $V_{DD}$ and $I_{DD}$ respectively                      |

| 3                               | -                               | Table "Ordering Information" removed                                                                                                                    |

| 10                              | 10                              | EA pin function description changed                                                                                                                     |

| -                               | 18                              | Description added for bit CSWO in SFR SYSCON                                                                                                            |

| 24                              | 24                              | Version Registers VR1, VR2 updated                                                                                                                      |

| 56                              | 56                              | Description of Absolute Maximum Ratings changed                                                                                                         |

| -                               | 57                              | Table "Operating conditions" added                                                                                                                      |

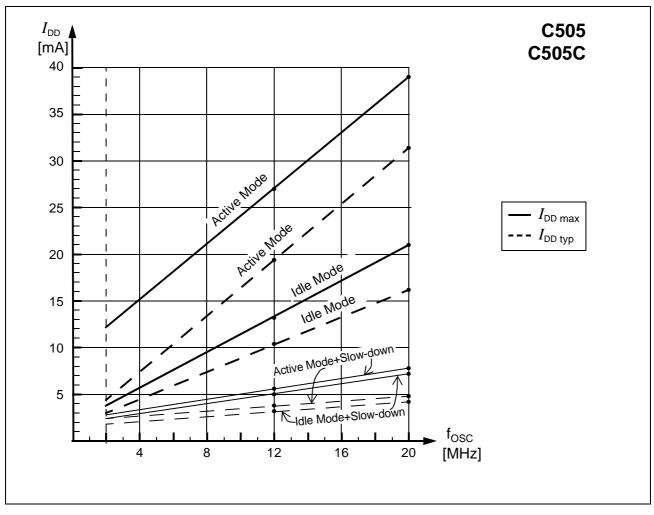

| several                         | several                         | I <sub>DD</sub> values for C505/C505C and C505A-4E/C505CA-4E updated                                                                                    |

| several                         | -                               | AC characteristics (12 MHz) removed                                                                                                                     |

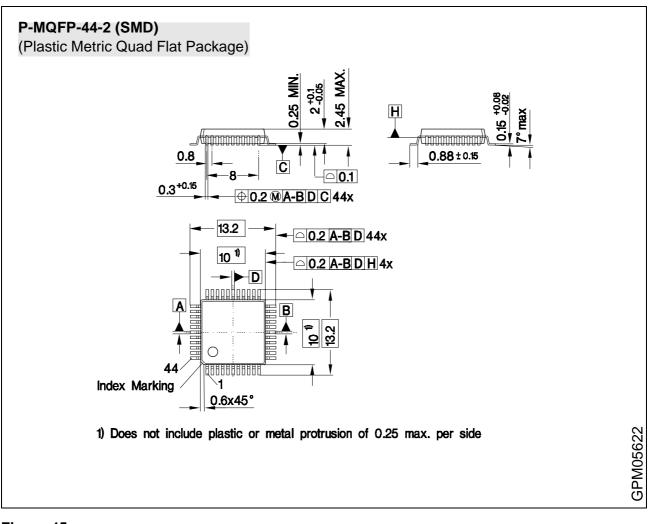

| 83                              | 83                              | Package number corrected by P-MQFP-44-2                                                                                                                 |

Controller Area Network (CAN): License of Robert Bosch GmbH

# We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

# 8-bit Single-Chip Microcontroller

C505 C505C C505A C505CA

### **Advance Information**

- Fully compatible to standard 8051 microcontroller

- Superset of the 8051 architecture with 8 datapointers

- Up to 20 MHz operating frequency

- 375 ns instruction cycle time @16 MHz

- 300 ns instruction cycle time @20 MHz (50 % duty cycle)

- On-chip program memory (with optional memory protection)

- C505(C)(A)-2R : 16K byte on-chip ROM

- C505A-4R/C505CA-4R: 32K byte on-chip ROM

- C505A-4E/C505CA-4E: 32K byte on-chip OTP

- alternatively up to 64k byte external program memory

- 256 byte on-chip RAM

- On-chip XRAM

- C505/C505C : 256 byte

- C505A/C505CA : 1K byte

(more features on next page)

| t Module   | Oscillator<br>Watchdog                                       |            | XRAM<br>505C: 256 byte<br>C505CA: 1K byte | RAM<br>256 byte | Port 0 |

|------------|--------------------------------------------------------------|------------|-------------------------------------------|-----------------|--------|

| Support    | A/D Converter<br>C505/C505C : 8-bit<br>C505A/C505CA : 10-bit | Timer<br>0 | C500<br>Core                              | 8-bit<br>USART  | Port 1 |

| Emulation  | Timer 2                                                      | Timer<br>1 | 8 Datapointers                            | 007             | Port 2 |

| n-Chip Emu | Full-CAN Controller<br>C505C/C505CA only                     | F          | Program Memor<br>C505(C)(A)-2R :          | ,               | Port 3 |

| O-uO       | Watchdog Timer                                               |            | 4R/C505CÁ-4R :<br>-4E/C505CA-4E           | 32K ROM         |        |

#### Figure 1 C505 Functional Units

Features (continued) :

- 32 + 2 digital I/O lines

- Four 8-bit digital I/O ports

- One 2-bit digital I/O port (port 4)

- Port 1 with mixed analog/digital I/O capability

- Three 16-bit timers/counters

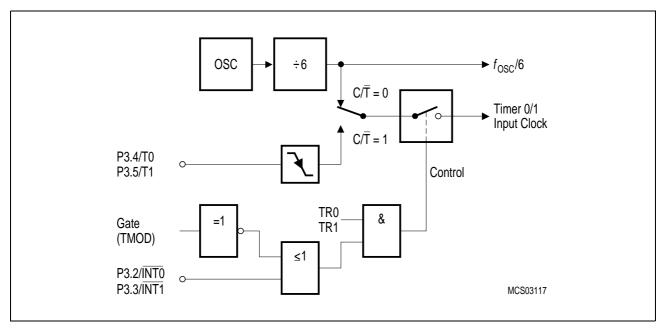

- Timer 0 / 1 (C501 compatible)

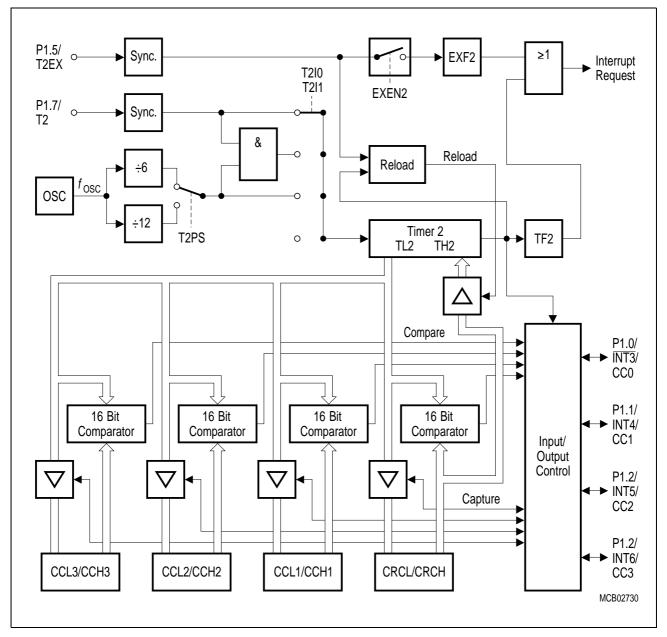

- Timer 2 with 4 channels for 16-bit capture/compare operation

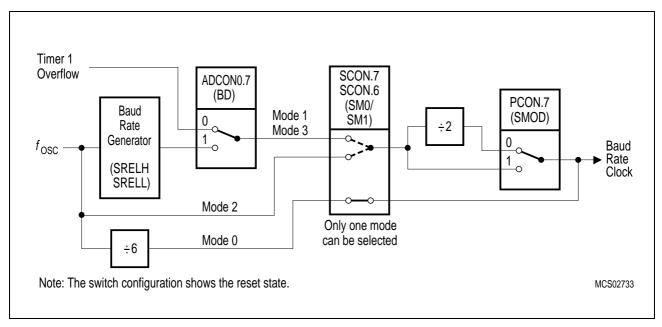

- Full duplex serial interface with programmable baudrate generator (USART)

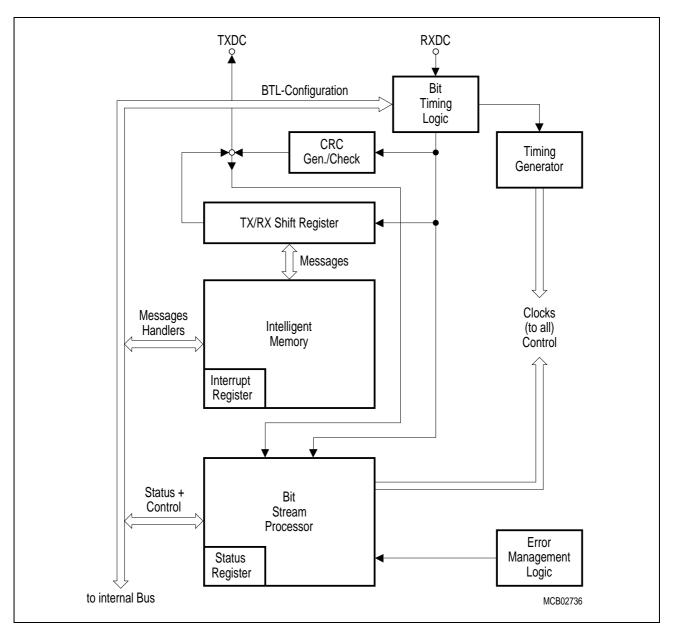

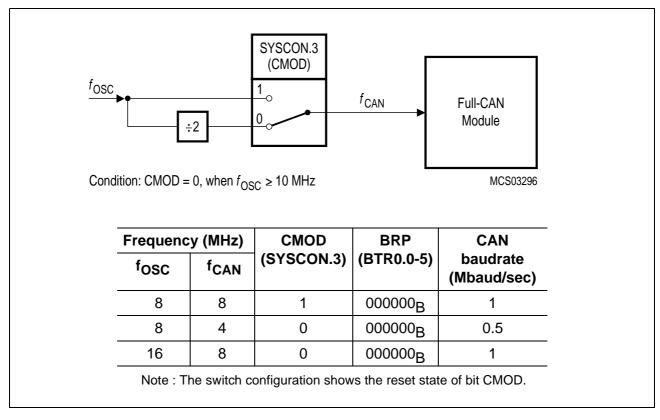

- Full CAN Module, version 2.0 B compliant (C505C and C505CA only)

- 256 register/data bytes located in external data memory area

- 1 MBaud CAN baudrate when operating frequency is equal to or above 8 MHz

- internal CAN clock prescaler when input frequency is over 10 MHz

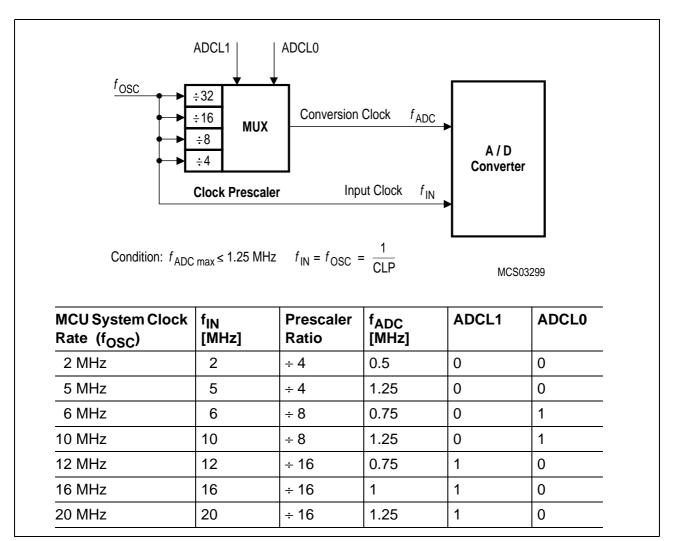

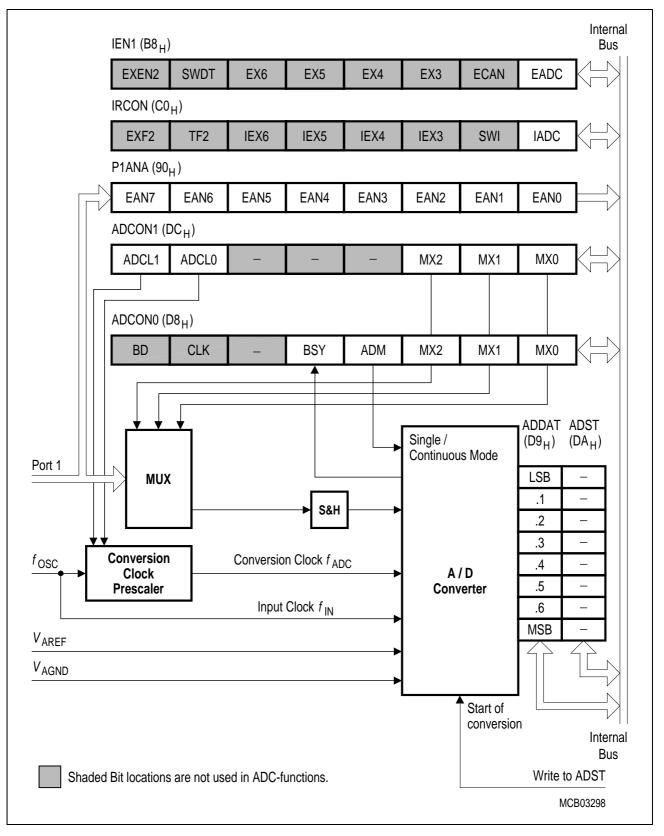

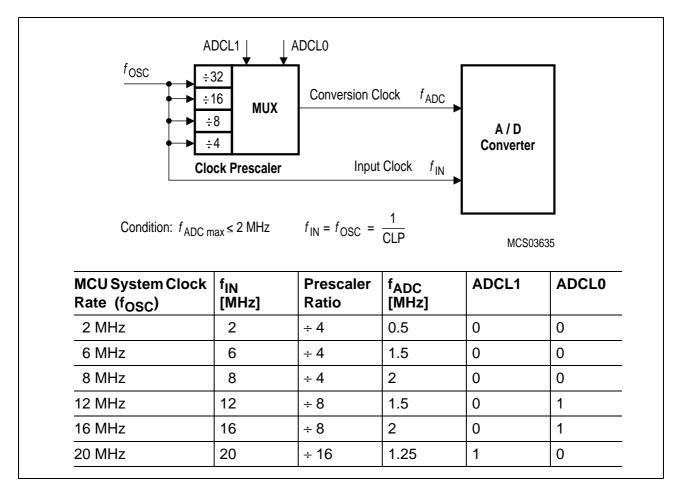

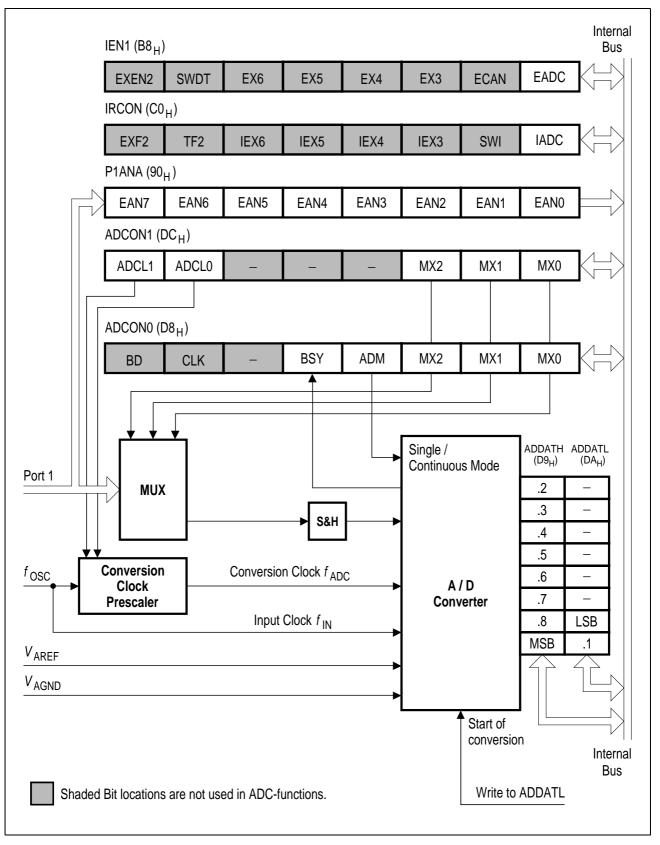

- On-chip A/D Converter

- up to 8 analog inputs

- C505/C505C : 8-bit resolution

- C505A/C505CA: 10-bit resolution

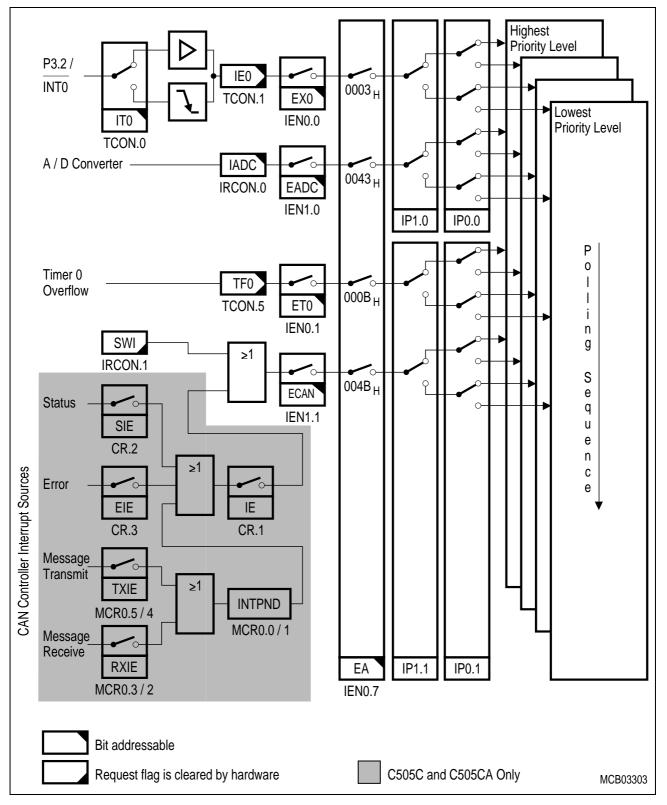

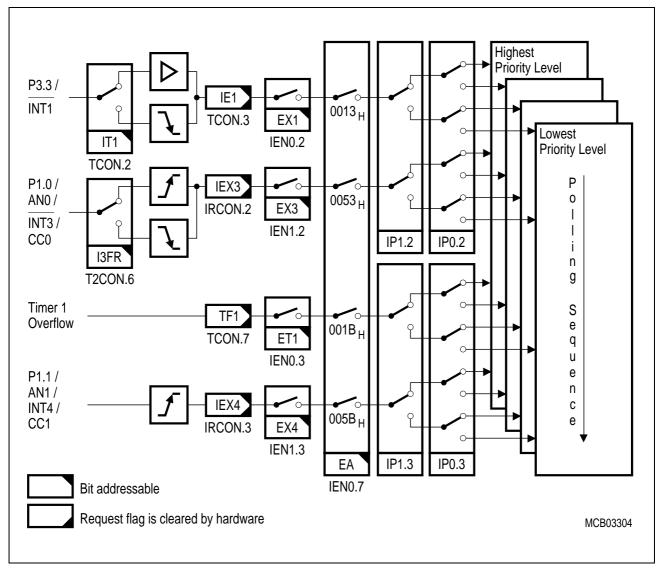

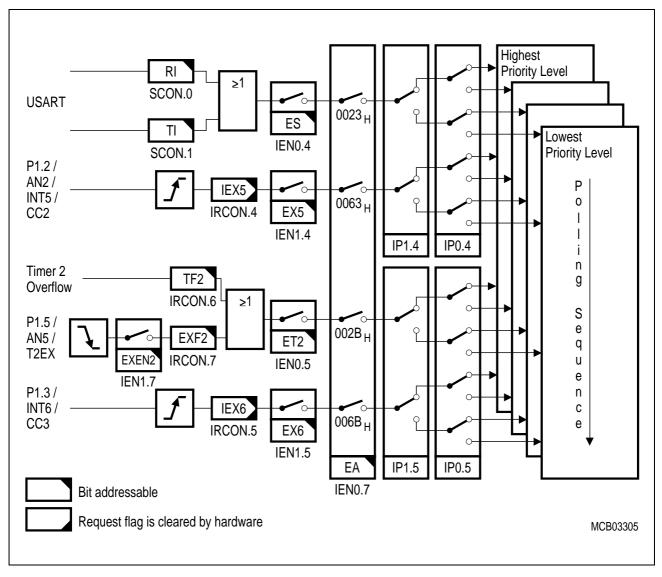

- Twelve interrupt sources with four priority levels

- On-chip emulation support logic (Enhanced Hooks Technology <sup>™</sup>)

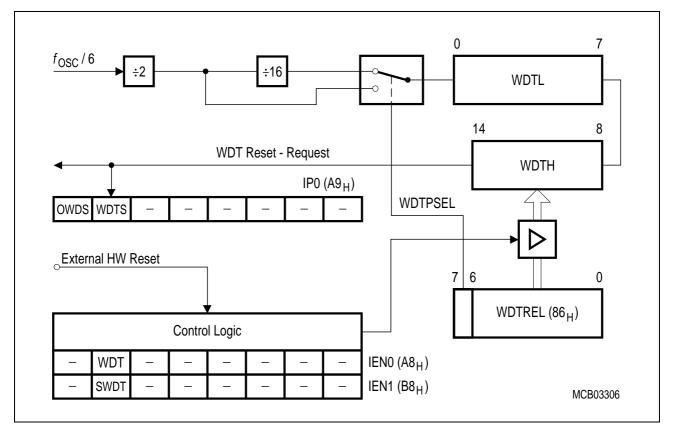

- Programmable 15-bit watchdog timer

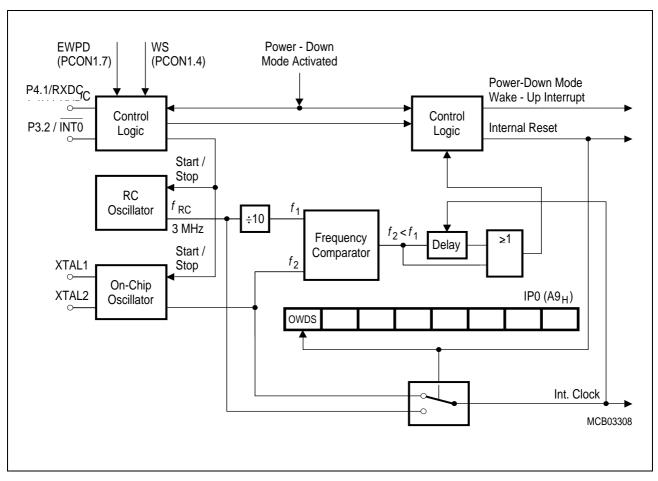

- Oscillator watchdog

- Fast power on reset

- Power Saving Modes

- Slow-down mode

- Idle mode (can be combined with slow-down mode)

- Software power-down mode with wake up capability through P3.2/INT0 or P4.1/RXDC pin

- P-MQFP-44 package

- Pin configuration is compatible to C501, C504, C511/C513-family

- Temperature ranges:

| SAB-C505 versions | $T_{A} = 0$ to 70 °C            |

|-------------------|---------------------------------|

| SAF-C505 versions | $T_{\rm A} = -40$ to 85°C       |

| SAH-C505 versions | $T_{\rm A}$ = -40 to 110°C      |

| SAK-C505 versions | $T_{A} = -40$ to $125^{\circ}C$ |

# Table 1Differences in Functionality of the C505 MCUs

| Device    | Internal Pro | ogram Memory | XRAM Size | A/D Converter | CAN          |

|-----------|--------------|--------------|-----------|---------------|--------------|

|           | ROM          | OTP          |           | Resolution    | Controller   |

| C505-2R   | 16K byte     | _            | 256 byte  | 8 Bit         | -            |

| C505-L    | -            | _            | 256 byte  | 8 Bit         | -            |

| C505C-2R  | 16K byte     | _            | 256 byte  | 8 Bit         | $\checkmark$ |

| C505C-L   | -            | _            | 256 byte  | 8 Bit         | $\checkmark$ |

| C505A-4R  | 32K byte     | _            | 1K byte   | 10 Bit        | -            |

| C505A-2R  | 16K byte     | _            | 1K byte   | 10 Bit        | -            |

| C505A-L   | _            | -            | 1K byte   | 10 Bit        | -            |

| C505CA-4R | 32K byte     | _            | 1K byte   | 10 Bit        |              |

| C505CA-2R | 16K byte     | -            | 1K byte   | 10 Bit        |              |

| C505CA-L  | -            | -            | 1K byte   | 10 Bit        | $\checkmark$ |

| C505A-4E  | -            | 32K byte     | 1K byte   | 10 Bit        | -            |

| C505CA-4E | _            | 32K byte     | 1K byte   | 10 Bit        | $\checkmark$ |

**Note:** The term C505 refers to all versions described within this document unless otherwise noted. However the term C505 may also be restricted by the context to refer to only CAN-less derivatives with 8-Bit ADC which are C505-2R and C505-L in this document.

**Note:** The term C505(C)(A)-2R, for simplicity, is used to stand for C505 16K byte ROM versions within this document which are C505-2R, C505C-2R, C505A-2R and C505CA-2R.

### **Ordering Information**

The ordering code for Infineon Technologies' microcontrollers provides an exact reference to the required product. This ordering code identifies:

- the derivative itself, i.e. its function set

- the specificed temperature rage

- the package and the type of delivery

For the available ordering codes for the C505 please refer to the "**Product information Microcontrollers**", which summarizes all available microcontroller variants.

Note: The ordering codes for the Mask-ROM versions are defined for each product after verification of the respective ROM code.

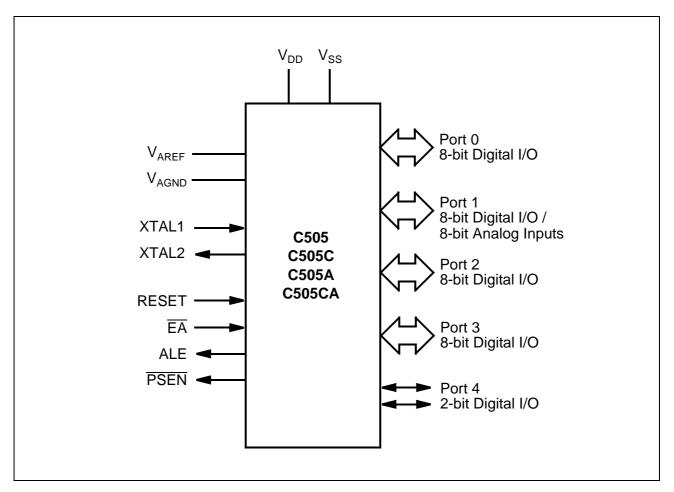

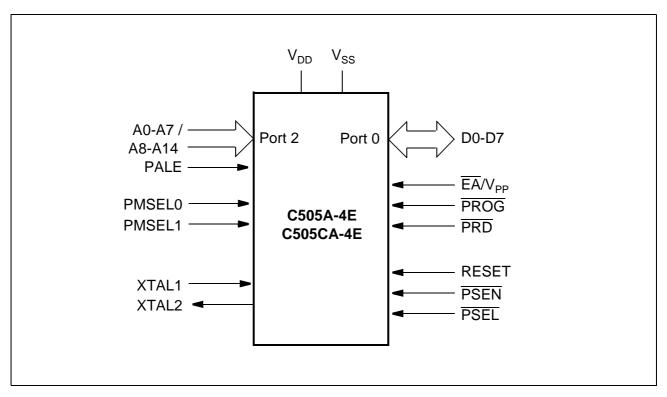

# Figure 2 Logic Symbol

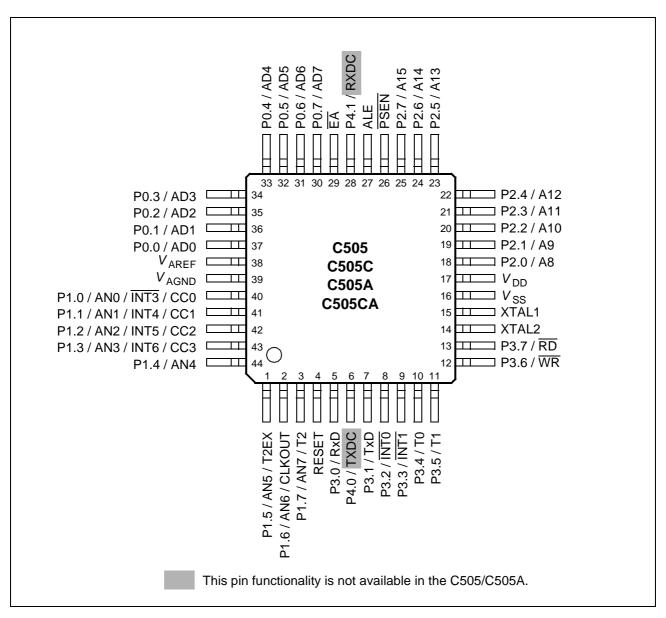

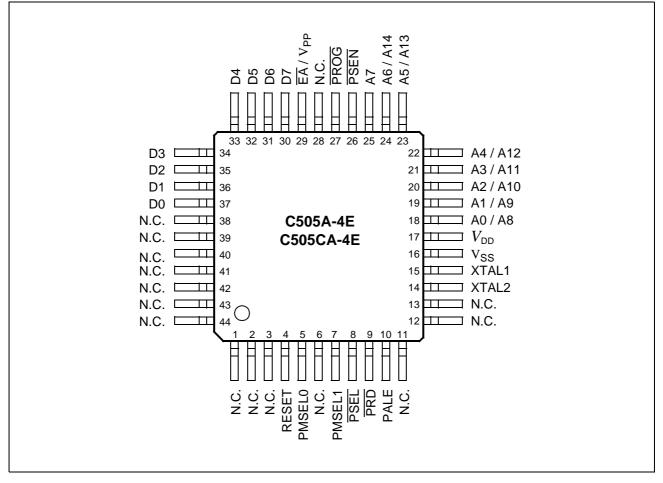

Figure 3 C505 Pin Configuration P-MQFP-44 Package (Top View)

| Symbol    | Pin Number | I/O<br>*) | Function                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                   |

|-----------|------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1.0-P1.7 | 40-44,1-3  | Ι/Ο       | arrangement. Port 1 pins<br>or as analog inputs of th<br>have 1's written to them<br>transistors and in that a<br>inputs, port 1 pins being<br>current ( $I_{IL}$ , in the DC<br>internal pullup transistor<br>used as analog inputs via<br>As secondary digital func<br>timer, clock, capture and<br>corresponding to a s<br>programmed to a one (1) | tions, port 1 contains the interrupt,<br>d compare pins. The output latch<br>secondary function must be<br>for that function to operate (except<br>). The secondary functions are |

|           | 40         |           | P1.0 / AN0 / INT3 / CC0                                                                                                                                                                                                                                                                                                                               | Analog input channel 0<br>interrupt 3 input /<br>capture/compare channel 0 I/O                                                                                                    |

|           | 41         |           | P1.1 / AN1 / INT4 / CC1                                                                                                                                                                                                                                                                                                                               | Analog input channel 1/<br>interrupt 4 input /<br>capture/compare channel 1 I/O                                                                                                   |

|           | 42         |           | P1.2 / AN2 / INT5 / CC2                                                                                                                                                                                                                                                                                                                               | Analog input channel 2 /<br>interrupt 5 input /<br>capture/compare channel 2 I/O                                                                                                  |

|           | 43         |           | P1.3 / AN3 / INT6 / CC3                                                                                                                                                                                                                                                                                                                               | Analog input channel 3<br>interrupt 6 input /<br>capture/compare channel 3 I/O                                                                                                    |

|           | 44         |           | P1.4 / AN4                                                                                                                                                                                                                                                                                                                                            | Analog input channel 4                                                                                                                                                            |

|           | 1          |           | P1.5 / AN5 / T2EX                                                                                                                                                                                                                                                                                                                                     | Analog input channel 5 / Timer 2<br>external reload / trigger input                                                                                                               |

|           | 2          |           | P1.6 / AN6 / CLKOUT                                                                                                                                                                                                                                                                                                                                   | Analog input channel 6 /<br>system clock output                                                                                                                                   |

|           | 3          |           | P1.7 / AN7 / T2                                                                                                                                                                                                                                                                                                                                       | Ánalog input channel 7 /<br>counter 2 input                                                                                                                                       |

|           |            |           |                                                                                                                                                                                                                                                                                                                                                       | order address byte during program<br>COM versions (i.e. C505(C)(A)-2R/                                                                                                            |

\*) I = Input

| Symbol    | Pin Number | I/O<br>*) | Function                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-----------|------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RESET     | 4          | 1         | <b>RESET</b><br>A high level on this pin for two machine cycle whil oscillator is running resets the device. An internal dif resistor to $V_{SS}$ permits power-on reset using on external capacitor to $V_{DD}$ . |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| P3.0-P3.7 | 5, 7-13    | I/O       | arrangement. F<br>pulled high by<br>state can be u<br>externally pull<br>characteristics)<br>The output late<br>must be program<br>(except for Tx                                                                  | asi-bidirectional port with internal pull-up<br>Port 3 pins that have 1's written to them are<br>the internal pull-up transistors and in that<br>sed as inputs. As inputs, port 3 pins being<br>ed low will source current ( $I_{IL}$ , in the DC<br>because of the internal pullup transistors.<br>ch corresponding to a secondary function<br>mmed to a one (1) for that function to operate<br>D and $\overline{WR}$ ). The secondary functions are<br>pins of port 3 as follows: |  |  |

|           | 5          |           | P3.0 / RxD                                                                                                                                                                                                         | Receiver data input (asynch.) or data input/output (synch.) of serial interface                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|           | 7          |           | P3.1 / TxD                                                                                                                                                                                                         | Transmitter data output (asynch.) or clock output (synch.) of serial interface                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|           | 8          |           | P3.2 / INT0                                                                                                                                                                                                        | External interrupt 0 input / timer 0 gate<br>control input                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|           | 9          |           | P3.3 / INT1                                                                                                                                                                                                        | External interrupt 1 input / timer 1 gate control input                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|           | 10         |           | P3.4 / T0                                                                                                                                                                                                          | Timer 0 counter input                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|           | 11         |           | P3.5 / T1                                                                                                                                                                                                          | Timer 1 counter input                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|           | 12         |           | P3.6 / WR                                                                                                                                                                                                          | WR control output; latches the data byte from port 0 into the external data memory                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|           | 13         |           | P3.7 / RD                                                                                                                                                                                                          | RD control output; enables the external data memory                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

\*) I = Input

| Symbol       | Pin Number | I/O<br>*)  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|--------------|------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P4.0<br>P4.1 | 6<br>28    | I/O<br>I/O | Port 4is a 2-bit quasi-bidirectional port with internal pull-up<br>arrangement. Port 4 pins that have 1's written to them are<br>pulled high by the internal pull-up transistors and in that<br>state can be used as inputs. As inputs, port 4 pins being<br>externally pulled low will source current ( $I_{IL}$ , in the DC<br>characteristics) because of the internal pullup transistors.<br>The output latch corresponding to the secondary function<br>RXDC must be programmed to a one (1) for that function to<br>operate. The secondary functions are assigned to the two<br>pins of port 4 as follows (C505C and C505CA only) :<br>P4.0 / TXDC<br>P4.1 / RXDC |  |

| XTAL2        | 14         | 0          | <b>XTAL2</b><br>Output of the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| XTAL1        | 15         | I          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

\*) I = Input

| Symbol    | Pin Number | I/O<br>*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

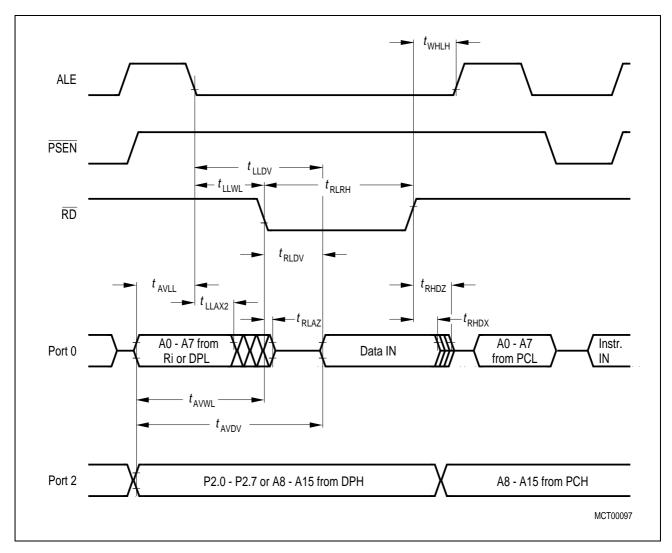

| P2.0-P2.7 | 18-25      | Ι/Ο       | <b>Port 2</b><br>is a an 8-bit quasi-bidirectional I/O port with internal pullup<br>resistors. Port 2 pins that have 1's written to them are pulled<br>high by the internal pullup resistors, and in that state can be<br>used as inputs. As inputs, port 2 pins being externally pulled<br>low will source current ( $I_{IL}$ , in the DC characteristics)<br>because of the internal pullup resistors. Port 2 emits the<br>high-order address byte during fetches from external<br>program memory and during accesses to external data<br>memory that use 16-bit addresses (MOVX @DPTR). In this<br>application it uses strong internal pullup transistors when<br>issuing 1s. During accesses to external data memory that<br>use 8-bit addresses (MOVX @Ri), port 2 issues the<br>contents of the P2 special function register and uses only<br>the internal pullup resistors. |

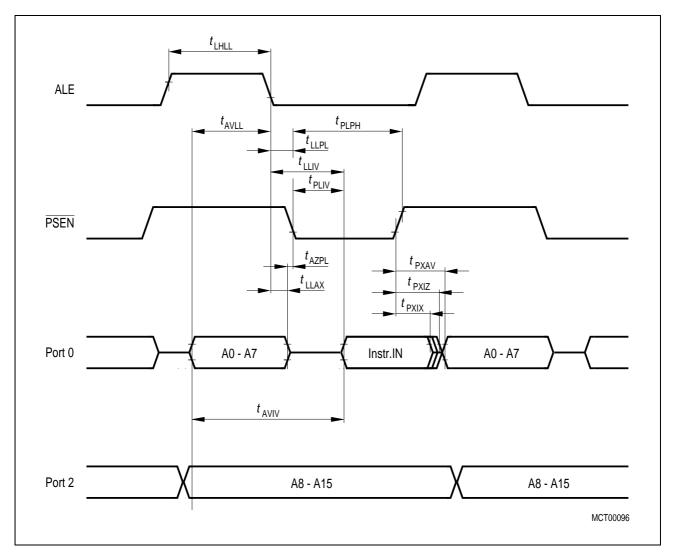

| PSEN      | 26         | 0         | The <b>Program Store Enable</b><br>output is a control signal that enables the external program<br>memory to the bus during external fetch operations. It is<br>activated every three oscillator periods except during<br>external data memory accesses. Remains high during<br>internal program execution. This pin should not be driven<br>during reset operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ALE       | 27         | 0         | The Address Latch Enable<br>output is used for latching the low-byte of the address into<br>external memory during normal operation. It is activated<br>every three oscillator periods except during an external data<br>memory access. When instructions are executed from<br>internal ROM or OTP (EA=1) the ALE generation can be<br>disabled by bit EALE in SFR SYSCON.<br>ALE should not be driven during reset operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

\*) I = Input

| Symbol            | Pin Number | I/O<br>*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------|------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĒĀ                | 29         | I         | <b>External Access Enable</b><br>When held at high level, instructions are fetched from the internal program memory when the PC is less than $4000_{\text{H}}$ (C505(C)(A)-2R) or $8000_{\text{H}}$ (C505A-4R/C505CA-4R/C505A-4E/C505CA-4E). When held at low level, the C505 fetches all instructions from external program memory.<br>For the C505 romless versions (i.e. C505-L, C505C-L, C505A-L and C505CA-L) this pin must be tied low.<br>For the ROM protection version $\overline{\text{EA}}$ pin is latched during reset.                               |

| P0.0-P0.7         | 37-30      | I/O       | <b>Port 0</b><br>is an 8-bit open-drain bidirectional I/O port. Port 0 pins that<br>have 1's written to them float, and in that state can be used<br>as high-impendance inputs. Port 0 is also the multiplexed<br>low-order address and data bus during accesses to external<br>program or data memory. In this application it uses strong<br>internal pullup transistors when issuing 1's.<br>Port 0 also outputs the code bytes during program<br>verification in the C505 ROM versions. External pullup<br>resistors are required during program verification. |

| V <sub>AREF</sub> | 38         | -         | Reference voltage for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>AGND</sub> | 39         | -         | Reference ground for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SS</sub>   | 16         | -         | Ground (0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>DD</sub>   | 17         | -         | Power Supply (+5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

\*) I = Input

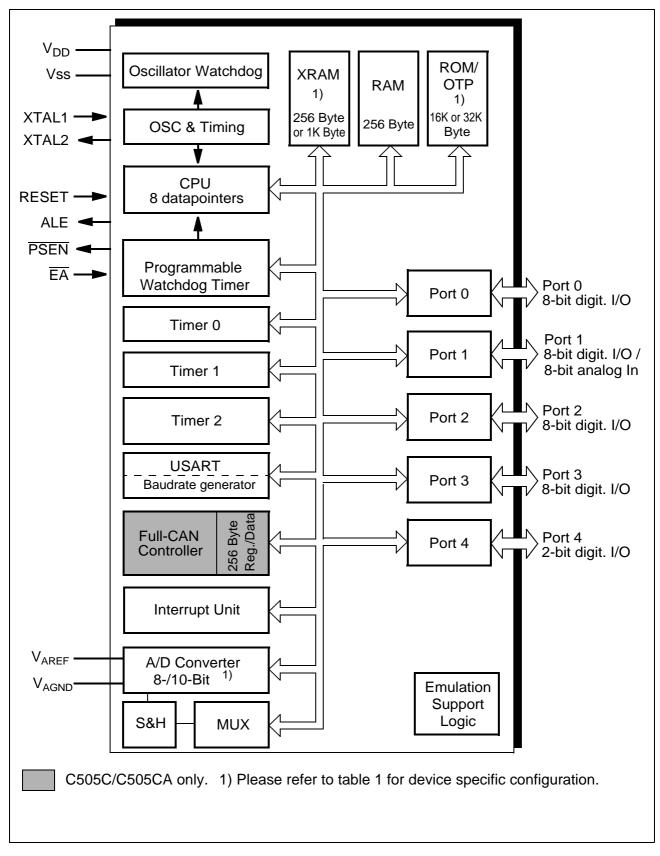

# Figure 4 Block Diagram of the C505/C505C/C505A/C505CA

# CPU

The C505 is efficient both as a controller and as an arithmetic processor. It has extensive facilities for binary and BCD arithmetic and excels in its bit-handling capabilities. Efficient use of program memory results from an instruction set consisting of 44 % one-byte, 41 % two-byte, and 15% three-byte instructions. With a 16 MHz crystal, 58% of the instructions are executed in 375 ns (20MHz: 300 ns).

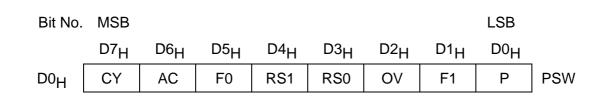

### Special Function Register PSW (Address D0<sub>H</sub>)

#### Reset Value : 00<sub>H</sub>

| Bit        | Functior                                                                                                                                                | Function                                                                   |                                                                |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| CY         | -                                                                                                                                                       | Carry Flag<br>Used by arithmetic instruction.                              |                                                                |  |  |  |  |

| AC         | -                                                                                                                                                       | Auxiliary Carry Flag<br>Used by instructions which execute BCD operations. |                                                                |  |  |  |  |

| F0         | General                                                                                                                                                 | Purpose F                                                                  | lag                                                            |  |  |  |  |

| RS1<br>RS0 | -                                                                                                                                                       |                                                                            | ect Control Bits<br>to select one of the four register banks.  |  |  |  |  |

|            | RS1                                                                                                                                                     | RS0                                                                        | Function                                                       |  |  |  |  |

|            | 0                                                                                                                                                       | 0                                                                          | Bank 0 selected, data address 00 <sub>H</sub> -07 <sub>H</sub> |  |  |  |  |

|            | 0                                                                                                                                                       | 1                                                                          | Bank 1 selected, data address 08 <sub>H</sub> -0F <sub>H</sub> |  |  |  |  |

|            | 1                                                                                                                                                       | 0                                                                          | Bank 2 selected, data address 10 <sub>H</sub> -17 <sub>H</sub> |  |  |  |  |

|            | 1                                                                                                                                                       | 1                                                                          | Bank 3 selected, data address 18 <sub>H</sub> -1F <sub>H</sub> |  |  |  |  |

| OV         |                                                                                                                                                         | Overflow Flag<br>Used by arithmetic instruction.                           |                                                                |  |  |  |  |

| F1         | General                                                                                                                                                 | General Purpose Flag                                                       |                                                                |  |  |  |  |

| Ρ          | Parity Flag           Set/cleared by hardware after each instruction to indicate an odd/even number of "one" bits in the accumulator, i.e. even parity. |                                                                            |                                                                |  |  |  |  |

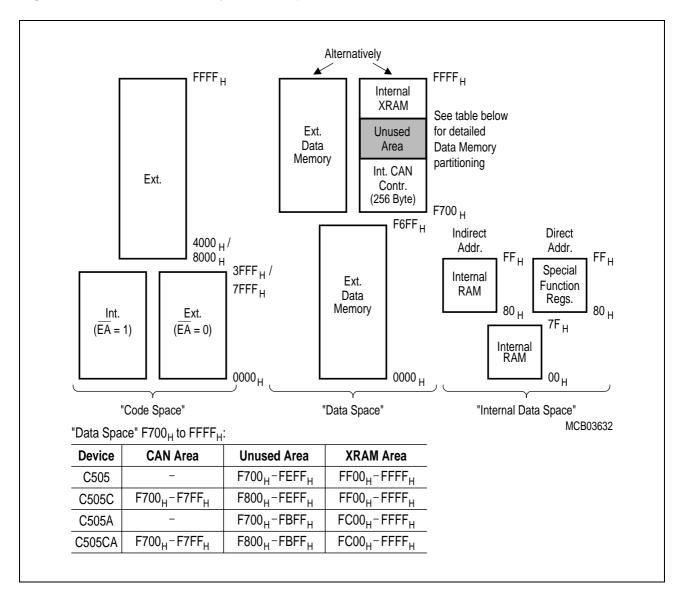

# **Memory Organization**

The C505 CPU manipulates operands in the following four address spaces:

On-chip program memory :16K byte ROM (C505(C)(A)-2R) or 32K byte ROM (C505A-4R/C505CA-4R) or

32K byte OTP (C505A-4E/C505CA-4E)

- Totally up to 64K byte internal/external program memory

- up to 64 Kbyte of external data memory

- 256 bytes of internal data memory

- Internal XRAM data memory :256 byte (C505/C505C)

1K byte (C505A/C505CA)

- a 128 byte special function register area

Figure 5 illustrates the memory address spaces of the C505 versions.

#### Figure 5 C505 Memory Map Memory Map

#### **Reset and System Clock**

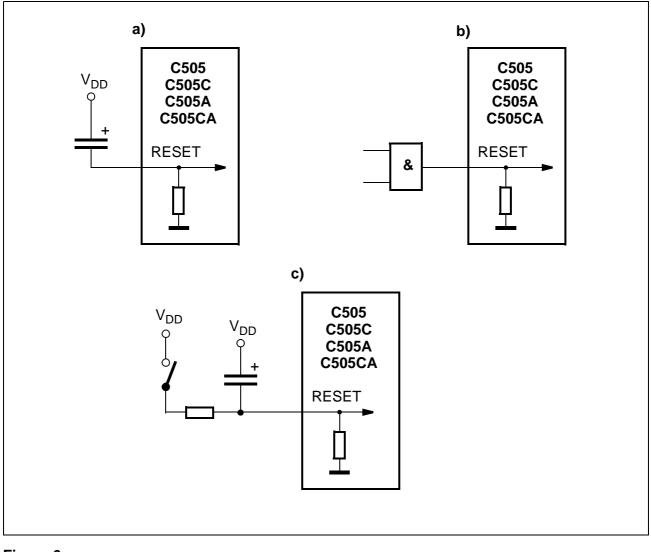

The reset input is an active high input at pin RESET. Since the reset is synchronized internally, the RESET pin must be held high for at least two machine cycles (12 oscillator periods) while the oscillator is running. A pulldown resistor is internally connected to  $V_{\rm SS}$  to allow a power-up reset with an external capacitor only. An automatic reset can be obtained when  $V_{\rm DD}$  is applied by connecting the RESET pin to  $V_{\rm DD}$  via a capacitor. **Figure 6** shows the possible reset circuitries.

Figure 6 Reset Circuitries

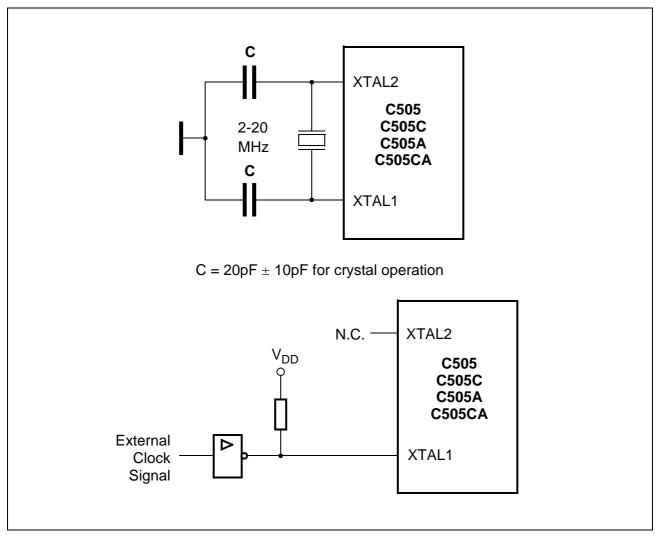

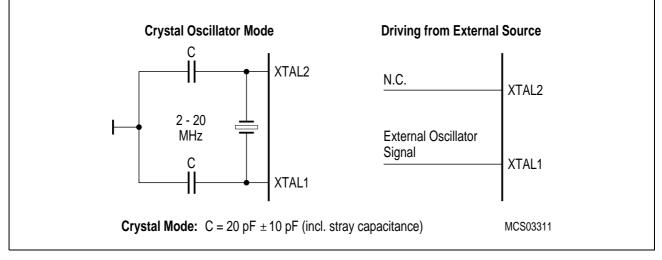

# Figure 7 shows the recommended oscillator circuits for crystal and external clock operation.

# Figure 7 Recommended Oscillator Circuitries

#### **Multiple Datapointers**

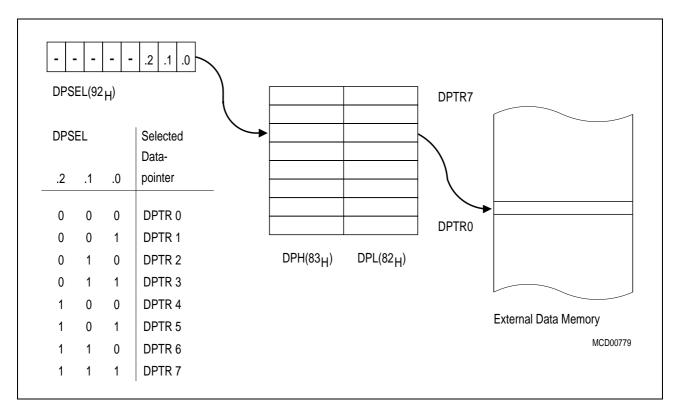

As a functional enhancement to the standard 8051 architecture, the C505 contains eight 16-bit datapointers instead of only one datapointer. The instruction set uses just one of these datapointers at a time. The selection of the actual datapointer is done in the special function regsiter DPSEL. **Figure 8** illustrates the datapointer addressing mechanism.

Figure 8 External Data Memory Addressing using Multiple Datapointers

### **Enhanced Hooks Emulation Concept**

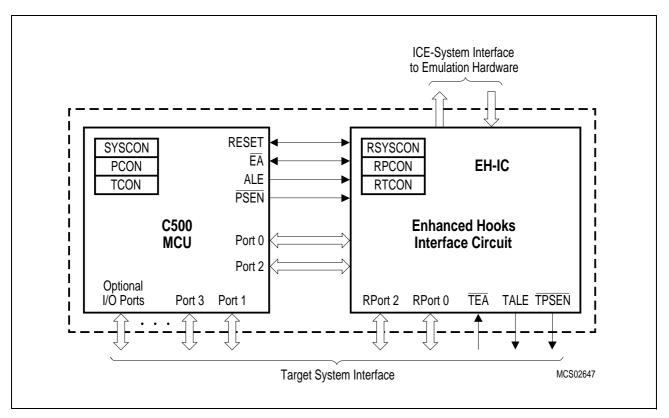

The Enhanced Hooks Emulation Concept of the C500 microcontroller family is a new, innovative way to control the execution of C500 MCUs and to gain extensive information on the internal operation of the controllers. Emulation of on-chip ROM based programs is possible, too.

Each production chip has built-in logic for the supprt of the Enhanced Hooks Emulation Concept. Therefore, no costly bond-out chips are necessary for emulation. This also ensure that emulation and production chips are identical.

The Enhanced Hooks Technology<sup>™ 1)</sup>, which requires embedded logic in the C500 allows the C500 together with an EH-IC to function similar to a bond-out chip. This simplifies the design and reduces costs of an ICE-system. ICE-systems using an EH-IC and a compatible C500 are able to emulate all operating modes of the different versions of the C500 microcontrollers. This includes emulation of ROM, ROM with code rollover and ROMless modes of operation. It is also able to operate in single step mode and to read the SFRs after a break.

# Figure 9

# Basic C500 MCU Enhanced Hooks Concept Configuration

Port 0, port 2 and some of the control lines of the C500 based MCU are used by Enhanced Hooks Emulation Concept to control the operation of the device during emulation and to transfer informations about the programm execution and data transfer between the external emulation hardware (ICE-system) and the C500 MCU.

<sup>1 &</sup>quot;Enhanced Hooks Technology" is a trademark and patent of Metalink Corporation licensed to Infineon Technologies.

# **Special Function Registers**

The registers, except the program counter and the four general purpose register banks, reside in the special function register area. The special function register area consists of two portions : the standard special function register area and the mapped special function register area. Five special function register of the C505 (PCON1,P1ANA, VR0, VR1, VR2) are located in the mapped special function register area. For accessing the mapped special function register area, bit RMAP in special function register SYSCON must be set. All other special function registers are located in the standard special function register area which is accessed when RMAP is cleared ("0").

The registers and data locations of the CAN controller (CAN-SFRs) are located in the external data memory area at addresses  $F700_{\text{H}}$  to  $F7FF_{\text{H}}$ .

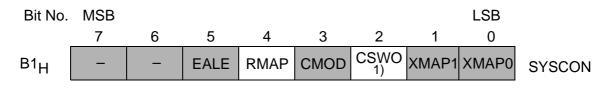

# Special Function Register SYSCON (Address B1<sub>H</sub>) Reset Value : XX100X01<sub>B</sub> (C505CA only) Reset Value : XX100001<sub>B</sub>

The functions of the shaded bits are not described here. 1) This bit is only available in the C505CA.

| Bit  | Function                                                                                                                                                                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMAP | <ul> <li>Special function register map bit</li> <li>RMAP = 0 : The access to the non-mapped (standard) special function register area is enabled.</li> <li>RMAP = 1 : The access to the mapped special function register area is enabled.</li> </ul> |

| CSWO | CAN Controller switch-off bit<br>CSWO = 0 : CAN Controller is enabled (default after reset).<br>CSWO = 1 : CAN Controller is switched off.                                                                                                           |

As long as bit RMAP is set, mapped special function register area can be accessed. This bit is not cleared by hardware automatically. Thus, when non-mapped/mapped registers are to be accessed, the bit RMAP must be cleared/set respectively by software.

All SFRs with addresses where address bits 0-2 are 0 (e.g.  $80_H$ ,  $88_H$ ,  $90_H$ ,  $98_H$ , ...,  $F8_H$ ,  $FF_H$ ) are bitaddressable.

The 52 special function registers (SFRs) in the standard and mapped SFR area include pointers and registers that provide an interface between the CPU and the other on-chip peripherals. The SFRs of the C505 are listed in **table 3** and **table 4**. In **table 3** they are organized in groups which refer to the functional blocks of the C505. The CAN-SFRs (applicable for the C505C and C505CA only) are also included in **table 3**. **Table 4** illustrates the contents of the SFRs in numeric order of their addresses. **Table 5** list the CAN-SFRs in numeric order of their addresses.

# Table 3Special Function Registers - Functional Blocks

| Block     | Symbol               | Name                                                                  | Address                       | Contents after<br>Reset                                                          |

|-----------|----------------------|-----------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------|

| CPU       | ACC                  | Accumulator                                                           | E0H <sup>1)</sup>             | 00 <sub>H</sub>                                                                  |

|           | В                    | B-Register                                                            | F0H <sup>1)</sup>             | 00 <sub>H</sub>                                                                  |

|           | DPH                  | Data Pointer, High Byte                                               | 83 <sub>H</sub>               | 00 <sub>H</sub>                                                                  |

|           | DPL                  | Data Pointer, Low Byte                                                | 82 <sub>H</sub>               | 00 <sub>H</sub>                                                                  |

|           | DPSEL                | Data Pointer Select Register                                          | 92 <sub>H</sub>               | XXXXX000 <sub>B<sup>3)</sup></sub>                                               |

|           | PSW                  | Program Status Word Register                                          | D0H <sup>1)</sup>             | 00 <sub>H</sub>                                                                  |

|           | SP                   | Stack Pointer                                                         | 81 <sub>H</sub>               | 07 <sub>H</sub>                                                                  |

|           | SYSCON <sup>2)</sup> | System Control Register                                               | B1 <sub>H</sub>               | XX100X01B <sup>3) 6)</sup><br>XX100001B <sup>3) 7)</sup>                         |

|           | VR0 4)               | Version Register 0                                                    | FC <sub>H</sub>               | C5H                                                                              |

|           | VR1 <sup>4)</sup>    | Version Register 1                                                    | FDH                           | 05 <sub>H</sub>                                                                  |

|           | VR2 <sup>4)</sup>    | Version Register 2                                                    | FEH                           | 5)                                                                               |

| A/D-      | ADCON0 <sup>2)</sup> | A/D Converter Control Register 0                                      | D8H <sup>1)</sup>             | 00X00000B 3)                                                                     |

| Converter | ADCON1               | A/D Converter Control Register 1                                      | DCH                           | 01XXX000 <sub>B</sub> <sup>3)</sup>                                              |

|           | ADDAT                | A/D Converter Data Reg. (C505/C505C)                                  | D9 <sub>H</sub>               | 00 <sub>H</sub>                                                                  |

|           | ADST                 | A/D Converter Start Reg. (C505/C505C)                                 | DAH                           | XX <sub>H</sub> <sup>3)</sup>                                                    |

|           | ADDATH               | A/D Converter High Byte Data Register<br>(C505A/C505CA)               | D9 <sub>H</sub>               | 00 <sub>H</sub>                                                                  |

|           | ADDATL               | A/D Converter Low Byte Data Register<br>(C505A/C505CA)                | DAH                           | 00XXXXXXB <sup>3)</sup>                                                          |

|           | P1ANA 2) 4)          | Port 1 Analog Input Selection Register                                | 90 <sub>H</sub>               | FFH                                                                              |

| Interrupt | IEN0 <sup>2)</sup>   | Interrupt Enable Register 0                                           | A8 <sub>H</sub> <sup>1)</sup> | 00 <sub>H</sub>                                                                  |

| System    | IEN1 <sup>2)</sup>   | Interrupt Enable Register 1                                           | B8H <sup>1)</sup>             | 00 <sub>H</sub>                                                                  |

|           | IP0 <sup>2)</sup>    | Interrupt Priority Register 0                                         | A9 <sub>H</sub>               | 00 <sub>H</sub>                                                                  |

|           | IP1                  | Interrupt Priority Register 1                                         | B9 <sub>H</sub>               | XX000000 <sub>B</sub> <sup>3)</sup>                                              |

|           | TCON <sup>2)</sup>   | Timer Control Register                                                | 88H <sup>1)</sup>             | 00 <sub>H</sub>                                                                  |

|           | T2CON <sup>2)</sup>  | Timer 2 Control Register                                              | C8 <sub>H</sub> <sup>1)</sup> | 00X00000B                                                                        |

|           | SCON <sup>2)</sup>   | Serial Channel Control Register                                       | 98H <sup>1)</sup>             | 00 <sub>H</sub>                                                                  |

|           | IRCON                | Interrupt Request Control Register                                    | C0H <sup>1)</sup>             | 00 <sub>H</sub>                                                                  |

| XRAM      | XPAGE                | Page Address Register for Extended on-chip<br>XRAM and CAN Controller | 91 <sub>H</sub>               | 00 <sub>H</sub>                                                                  |

|           | SYSCON <sup>2)</sup> | System Control Register                                               | B1 <sub>H</sub>               | XX100X01 <sub>B</sub> <sup>3) 6)</sup><br>XX100001 <sub>B</sub> <sup>3) 7)</sup> |

1) Bit-addressable special function registers

2) This special function register is listed repeatedly since some bits of it also belong to other functional blocks.

3) "X" means that the value is undefined and the location is reserved

4) This SFR is a mapped SFR. For accessing this SFR, bit RMAP in SFR SYSCON must be set.

5) The content of this SFR varies with the actual step of the C505 (eg. 01<sub>H</sub> for the first step)

6) C505 / C505A/C505C only

7) C505CA only

# Table 3 Special Function Registers - Functional Blocks (cont'd)

| ChannelPCON 2)Power Control Register $87_{H}$ $00_{H}$ SBUFSerial Channel Buffer Register $99_{H}$ $XX_{H}^{3)}$ SCONSerial Channel Control Register $98_{H}^{1)}$ $00_{H}$ SRELLSerial Channel Reload Register, low byte $AA_{H}$ $D9_{H}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 000 <sub>B</sub> <sup>3)</sup>  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 000 <sub>B</sub> <sup>3)</sup>  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 000 <sub>B</sub> <sup>3)</sup>  |

| P2<br>P3<br>P4Port 2<br>Port 3<br>P4Port 3<br>Port 4A0H 1)<br>B0H 1)<br>E8H 1)FFH<br>FFH<br>FFH<br>E8H 1)Serial<br>ChannelADCON02)<br>PCON2)A/D Converter Control Register 0<br>Power Control RegisterD8H 1)<br>87H<br>00H<br>99H00X00<br>87H<br>99HSerial<br>SCON<br>SERELL<br>SRELL<br>SRELLSerial Channel Buffer Register<br>Serial Channel Reload Register, low byte<br>SRELL<br>SRELL<br>Serial Channel Reload Register, low byte<br>SRELL<br>Serial Channel Reload Register, high byteBAH<br>AAH<br>D9H<br>BAHXXXX2Timer 0/<br>Timer 1TCON<br>Timer 0/1 Control Register<br>Timer 1, High Byte<br>TL0<br>TL0<br>Timer 1, Low Byte<br>TMOD80H<br>OH<br>BAH<br>OH<br>BAH00H<br>BAH<br>OH<br>BAH                                                                                                                            | 000 <sub>B</sub> <sup>3)</sup>  |

| P3<br>P4Port 3<br>Port 4B0H 1)<br>E8H 1)FFH<br>XXXXSerial<br>ChannelADCON02)<br>PCON2)A/D Converter Control Register 0<br>Power Control RegisterD8H 1)<br>00X0000X00<br>87HSerial<br>SBUFPCON2)<br>Serial Channel Buffer Register99H<br>99H<br>XXH3)XXH3)<br>99H<br>99H<br>SRELL00H<br>Serial Channel Control RegisterSRELL<br>SRELLSerial Channel Control Register<br>SRELL98H 1)<br>98H 1)00H<br>00H<br>AAHTimer 0/<br>Timer 1TCON<br>Th0Timer 0/1 Control Register<br>Timer 1, High Byte<br>TL0<br>TL0<br>TL088H 1)<br>Timer 1, Low Byte<br>Timer 1, Low Byte80H<br>00H<br>80H<br>80H                                                                                                                                                                                                                                       | 000 <sub>B</sub> <sup>3)</sup>  |

| Serial<br>ChannelADCON0 2)<br>PCON 2)A/D Converter Control Register 0<br>Power Control RegisterD8 <sub>H</sub> 1)<br>87 <sub>H</sub> 00X00<br>87 <sub>H</sub> SBUF<br>SCON<br>SRELL<br>SRELHSerial Channel Buffer Register<br>Serial Channel Control Register99 <sub>H</sub><br>99 <sub>H</sub> XX <sub>H</sub> 3)<br>98 <sub>H</sub> 1)<br>00 <sub>H</sub> Timer 0/<br>Timer 1TCON<br>TH0Timer 0/1 Control Register<br>Serial Channel Reload Register, high byte88 <sub>H</sub> 1)<br>8C <sub>H</sub> 00 <sub>H</sub><br>99 <sub>H</sub> Timer 1TH0<br>TH1Timer 0, High Byte<br>Timer 1, High Byte88 <sub>H</sub> 1)<br>8D <sub>H</sub> 00 <sub>H</sub><br>90 <sub>H</sub> TL0<br>TL0<br>TMODTimer 1, Low Byte<br>Timer Mode Register88 <sub>H</sub><br>8D <sub>H</sub><br>90 <sub>H</sub> 00 <sub>H</sub><br>80 <sub>H</sub> | 000 <sub>B</sub> <sup>3)</sup>  |

| ChannelPCON 2)Power Control Register $87_{H}$ $00_{H}$ SBUFSerial Channel Buffer Register $99_{H}$ $XX_{H}^{3}$ SCONSerial Channel Control Register $98_{H}^{1}$ $00_{H}$ SRELLSerial Channel Reload Register, low byte $8A_{H}$ $D9_{H}$ SRELHSerial Channel Reload Register, high byte $BA_{H}$ $XXXXX$ Timer 0/TCONTimer 0/1 Control Register $88_{H}^{1}$ $00_{H}$ Timer 1TH0Timer 0, High Byte $8C_{H}$ $00_{H}$ TL0Timer 1, High Byte $8D_{H}$ $00_{H}$ TL1Timer 1, Low Byte $8B_{H}$ $00_{H}$ TMODTimer Mode Register $8B_{H}$ $00_{H}$                                                                                                                                                                                                                                                                                 | _                               |

| ChannelPCON 2)Power Control Register $87_{H}$ $00_{H}$ SBUFSerial Channel Buffer Register $99_{H}$ $XX_{H}^{3}$ SCONSerial Channel Control Register $98_{H}^{1}$ $00_{H}$ SRELLSerial Channel Reload Register, low byte $8A_{H}$ $D9_{H}$ SRELHSerial Channel Reload Register, high byte $BA_{H}$ $XXXXX$ Timer 0/TCONTimer 0/1 Control Register $88_{H}^{1}$ $00_{H}$ Timer 1TH0Timer 0, High Byte $8C_{H}$ $00_{H}$ TL0Timer 1, High Byte $8D_{H}$ $00_{H}$ TL1Timer 1, Low Byte $8B_{H}$ $00_{H}$ TMODTimer Mode Register $8B_{H}$ $00_{H}$                                                                                                                                                                                                                                                                                 | _                               |

| SBUF<br>SCON<br>SRELL<br>SRELHSerial Channel Buffer Register<br>Serial Channel Control Register99<br>98<br>H1)XXH3)<br>00H<br>AAH<br>BAHTimer 0/<br>Timer 0/TCON<br>Timer 0, High ByteSerial Channel Reload Register, high byteBAH<br>BAHXXXXX<br>XXXXXTimer 1TH0<br>Timer 0, High ByteTimer 0, High Byte<br>BAHBOH<br>00H<br>00H00H<br>00H<br>00HTIL0<br>TL1<br>TIMODTimer 0, Low Byte<br>Timer 1, Low ByteBAH<br>00H<br>00H<br>00H00H<br>00H<br>00H<br>00H<br>00H                                                                                                                                                                                                                                                                                                                                                            |                                 |

| SCON<br>SRELL<br>SRELHSerial Channel Control Register<br>Serial Channel Reload Register, low byte<br>Serial Channel Reload Register, high byte98H 1)<br>AAH<br>D9H<br>BAH00H<br>AAH<br>D9H<br>BAHTimer 0/<br>Timer 0/TCON<br>Timer 0/1 Control Register<br>Timer 1, High Byte88H 1)<br>8CH<br>00H<br>8CH00H<br>00H<br>00H<br>8CH<br>00H<br>00H<br>8CHTimer 1<br>TH0<br>TH1Timer 0, High Byte<br>Timer 1, High Byte80H<br>80H<br>00H<br>80H00H<br>00H<br>80H<br>00H<br>80HTL0<br>TL1<br>TMODTimer 1, Low Byte<br>Timer Mode Register88H<br>80H<br>80H<br>00H<br>80H00H<br>80H<br>80H<br>80H                                                                                                                                                                                                                                     |                                 |

| SRELL<br>SRELHSerial Channel Reload Register, low byte<br>Serial Channel Reload Register, high byteAA <sub>H</sub><br>BA <sub>H</sub> D9 <sub>H</sub><br>XXXXTimer 0/<br>Timer 1TCONTimer 0/1 Control Register88 <sub>H</sub> <sup>1)</sup> 00 <sub>H</sub><br>8C <sub>H</sub> 00 <sub>H</sub> Timer 1TH0Timer 0, High Byte8C <sub>H</sub> 00 <sub>H</sub> TH1Timer 1, High Byte8D <sub>H</sub> 00 <sub>H</sub> TL0Timer 0, Low Byte8A <sub>H</sub> 00 <sub>H</sub> TL1Timer 1, Low Byte8B <sub>H</sub> 00 <sub>H</sub> TMODTimer Mode Register89 <sub>H</sub> 00 <sub>H</sub>                                                                                                                                                                                                                                                 |                                 |

| SRELHSerial Channel Reload Register, high byteBAHXXXXTimer 0/TCONTimer 0/1 Control Register88H <sup>1)</sup> 00HTimer 1TH0Timer 0, High Byte8CH00HTH1Timer 1, High Byte8DH00HTL0Timer 0, Low Byte8AH00HTL1Timer 1, Low Byte8BH00HTMODTimer Mode Register89H00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |

| Timer 1TH0Timer 0, High Byte8CH00HTH1Timer 1, High Byte8DH00HTL0Timer 0, Low Byte8AH00HTL1Timer 1, Low Byte8BH00HTMODTimer Mode Register89H00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | XX11 <sub>B</sub> <sup>3)</sup> |

| Timer 1TH0Timer 0, High Byte8CH00HTH1Timer 1, High Byte8DH00HTL0Timer 0, Low Byte8AH00HTL1Timer 1, Low Byte8BH00HTMODTimer Mode Register89H00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |

| TH1Timer 1, High Byte8DH00HTL0Timer 0, Low Byte8AH00HTL1Timer 1, Low Byte8BH00HTMODTimer Mode Register89H00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |

| TL0Timer 0, Low Byte8AH00HTL1Timer 1, Low Byte8BH00HTMODTimer Mode Register89H00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |

| TL1Timer 1, Low Byte8BH00HTMODTimer Mode Register89H00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

| TMODTimer Mode Register89H00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |